Recent searches

Search options

#dec

@revspace After a few days of work, implementing 3 missing libc functions, repairing an extra 4MB of RAM, hacking around toolchain issues, we finally got Lynx 2.8.2 compiled and running on the VAX-11/750 (in 4.3 BSD Quasijarus)! That means we got to browse the (non-HTTPS) web using no equipment or parts newer than 1986 this side of the network (besides the AUI 10Base-T phy).

Decided to display the VAX-11/750 at the @revspace open day yesterday. All the hard work repairing it seems to have paid off, managed to get 14 hours of uptime out of it before shutting it down at the end of the day! #unix #retrocomputing #dec #vax11 #minicomputer #unixhistory #bsd

"Reading Museum is hosting an exhibition marking more than 60 years since Digital Equipment Corporation (DEC) opened its first UK office...

The exhibition occupies much of the Sir John Madejski Art Gallery and, as well as some pre-DEC artifacts, has a range of hardware on show, from PDP racks and panels, through retro terminals, to VAX machines, a few of which still bear hopeful "Alpha ready" stickers. The walls show a timeline and quotes from the people involved, with screens to tell the story."

The one photo on that page makes me want to go!!!!

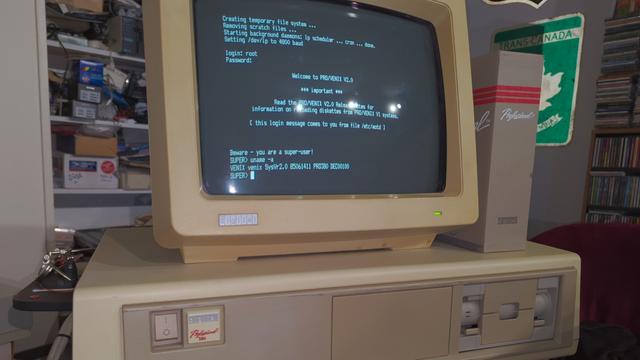

Booting a Desktop PDP-11 - Ever heard of VENIX? There were lots of variants of Unix back in the day, and VENI... - https://hackaday.com/2025/03/23/booting-a-desktop-pdp-11/ #retrocomputing #pdp-11 #unix #dec

Hi all, we did our annual PDP-12 demo in Dr. Ted Pedersen's architecture class on Tuesday, and it went really well.

In cleaning up / reorganizing after showing off our artifacts, I realized that we have something that I haven't seen on @bitsavers, but I maybe just didn't know where to look. It's a big poster of PDP-12 instructions -- it's kind of like the pocket reference in poster format. It is about 9.5x30 inches (24x76 cm). I scanned it in two pieces on the office machine and stitched it together with GIMP. I'll try to make a PDF version with OCR text. @bitsavers #vintagecomputing #retrocomputing #pdp12 #pdp #dec #umdpdp12

Reading Museum is hosting an exhibition marking more than 60 years since Digital Equipment Corporation (DEC) opened its first UK office

Well @retrobytes goes very nerdy¹ about the DEC PDP-10 and builds a replica in the form of a PiDP-10 in an epic soldering montage.

He also waxes lyrical about the TOPS-10 OS for the PDP-10 and it's ancestry to CP/M, MS-DOS and via another route to Microsoft BASIC and a lot lot more more!

Connections going every which way that even James Burke would appreciate

¹ Clearly the best kind of nerdy

You may use this #DEC #VT100 #terminal #beep as you wish.

#Retrocomputing #feep #pcspeaker

@larsbrinkhoff “The launch of Digital Equipment Corporation’s PDP-1 (Programmed Data Processor-1) computer in 1959 marked a radical shift in the philosophy of computer design.

This on-line exhibition covers the history of this groundbreaking computer and the Computer History Museum’s recent restoration of a PDP-1 to working order.”

#DEC / #PDP1 / #PDP / #BBN / #MIT <https://www.computerhistory.org/pdp-1/>

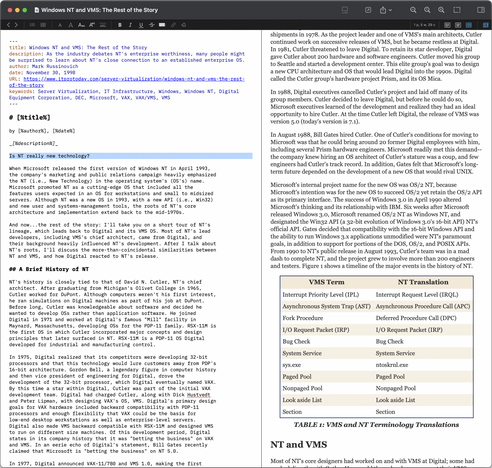

Did I just do a #Markdown conversion of Mark Russinovich’s seminal 1998 article on #WindowsNT (and by extension, all modern versions of #MicrosoftWindows)’ debt to #DEC’s #VMS #OperatingSystem? Just so I could have a decent copy apart from the dusty carried-over archived version at https://www.ITProToday.com/server-virtualization/windows-nt-and-vms-the-rest-of-the-story ?

Why yes, yes I did. Why not?

Some artifacts from an active network closet down the hall, at the office in DC: a USRobotics 33.6 modem and a DEC VT520

#VT520 #DEC vitangecomputing #retrocomputing #artifacts #foundatwork #network #closet #modem #USRobotics #CRT #terminal #photo

Original, from my student placement year in 1993. A DEC sales rep handed them out but everyone was made to give them back as there were rules (ha!) against gifts from vendors. As I wasn’t really an employee I kept quiet, and kept the ruler.

Dave Minter shared his experience in the 1990s with the precursors of modern email, discussion boards, instant messaging, and social systems. He told his story as a student in a DEC-centric world at a UK university linked to JANET and later to the Internet.

I'd been a member of #SDF for about a year or so when I posted to #BBoard to get rid of a load of 10-12 year old #DEC workstations and a server that my wife's ex left in his house. Someone responded, and we met down in Lewisville or somewhere. I don't know if that person was able to get them going. I have this hope/wish that they're still running somewhere and now 30ish-year-old computers living their lives.

@jfmezei :How long are data blocks for each entry in the in-CPU cache? 64 bits ? 128 bytes ? 1 page ?

It varies. Most implementations will use one cache block size at a time at a given cache level, but that size and the size and the organization of the caches varies.

:Does this vary from architecture to architecture or even inside an architecture?

Yes. Alpha caching varied by processor and by implementation, all within the limits of the Alpha architecture.

:Is it totally transparent when writing at OS level?

Totally transparent? No.

Details, such as what was locally called word tearing, alignment, memory timing, and memory lock processing, all get involved.

Similar requirements can arise in apps.

There are a few other wrinkles I’d prefer to not meet again, too.

Mostly transparent? Yes.

:And in multi core with coherent caches, when a core does a write to RAM, does memory controller propagate this to all other cores in case they have it cached? or does memory controller know which core has what in cache and send only relevant updates?

It depends. Most of what I’ve met will mark the cache contents as being invalid, and will await the next opportunity to wait for main memory to load the data, or to wait for a load from L3, or such. I can’t recall ever working on a cache-coherent multiprocessor that tried to reload the cache everywhere.

Alpha could load cache speculatively, or explicitly, or evict as needed.

http://bitsavers.org/pdf/dec/alpha/system_reference/Alpha_System_Reference_Manual_Version_7_1997.pdf

WP has a reasonable description, as well:

https://en.wikipedia.org/wiki/Cache_(computing)

Deeper still:

https://www.cs.swarthmore.edu/~kwebb/cs31/f18/memhierarchy/caching.html

More for amusement, figures 5 and 6 nicely show the shifting scale of the complexity of modern computer systems:

https://www.computer.org/csdl/journal/ts/2021/06/08704965/19HKUhJMVAQ

#digitalequipment #dec

#alpha #computerarchitecture #retrocomputing

UNIX Archaeology Turns Up 1972 “V2 Beta” https://hackaday.com/2025/02/20/unix-archaeology-turns-up-1972-v2-beta/ #Retrocomputing #SoftwareHacks #PDP-11/20 #unix #DEC

@Holberg It is not, it's now the "DCU Centre," after a local bank, which bizarrely is the surviving employee credit union of the long-defunct Digital Equipment Corp.

I feel like Mastodon people might appreciate that oddball piece of #ComputerScience #history.

2/ This is why I have never been a fan of Linux, people should be writing their own OSs

As an aside, I found this #USENET thread with some familiar names from 1987 about porting Minix to the Atari - I assume that would have been the ST then.

https://www.linux.co.cr/unix-source-code/review/1987/0108.html

Dizzy 0069 Stiff Assed Crip

Dizzy 0069 Stiff Assed Crip